# EXPERIMENTAL REALIZATION OF A RESISTIVE SINGLE FLUX QUANTUM LOGIC CIRCUIT

V. P. Koshelets, K. K. Likharev, V. V. Migulin, O. A. Mukhanov, G. A. Ovsyannikov, V. K. Semenov, I. L. Serpuchenko, and A. N. Vystavkin Institute of Radio Engineering and Electronics, USSR Academy of Sciences,

Marx Avenue 18, Moscow GSP-3, USSR

Department of Physics, Moscow State University,

Moscow 119899 GSP, USSR

#### Abstract

An integrated circuit including all basic components of the recently suggested Resistive Single Flux Quantum (RSFQ) logic family has been designed, fabricated and tested successfully. The circuit includes a generator of periodic SFQ pulses, four buffer/amplifier stages for splitting, channeling and regeneration of the pulses, a detector/load stage, and universal RSFQ logic gate (here performing the NOT function). The  $10\,\mathrm{Mm}$ design rule circuit employs 13 active Nb - Al2O3 - Nb Josephson junctions with the critical current density ~0.5 kA/cm<sup>2</sup>, externally shunted by Mo resistors with R 1 Ohm. The shunting provided critical damping of the junctions ( $\beta_c \lesssim 1$ ) and reasonable (~500  $\mu$ V)  $I_cR$  product. The circuit operation has been tested by measurement of dc voltages  $\overline{\mathtt{V}}_{\mathbf{i}}$  across various Josephson junctions as functions of the dc current through the pulse generator. Correct and stable operation of the circuit for the clock frequencies from 0 to ~30 GHz has been demonstra-

#### Introduction

Recently, much attention has been attracted to a new type of the Josephson junction digital circuits where the binary information is stored in form of the single flux quanta (SFQ), and transmitted in form of short voltage pulses with the area

$$\int V(t) dt \simeq \Phi_0. \tag{1}$$

In contrast with earlier SFQ logic circuits (using, é. g., the Josephson transmission lines¹, the "flux shuttle" shift registers² or the parametric quantrons³/>) in the new circuits the SFQ pulses could be transferred along resistive rather than purely inductive lines, and later regenerated to their nominal amplitude (Eq 1) by the next circuit stages. The simplest amplification stage of this kind consists of just a single overdamped ( $\beta_{\rm C} < 1$ ) Josephson junction biased with a dc current I slightly below its critical value I<sub>C</sub> (some more complex circuits with the similar junctions  $^{7-11}$  can be even more suitable for this purpose). Apparently the first device using this principle, the binary counter, has been suggested by Silver and coathors  $^{5}$ . Later this device has been tested  $^{6}$ ,  $^{7}$  to be operable at frequencies of the input pulses up to  $\sim 100$  GHz  $^{6}$ .

This success has motivated invention of more complex logic circuits; for example an AND gate based on the two - junction interferometer was suggested in Ref. 7. This gate, however, could hardly be practical because it requires time coincidence of the supershort (picosecond) SFQ pulses (Eq 1). In order to get rid of this problem, a new major step, a more precise defenition of representation of the digital imformation, was required.

This step was made by suggestion 9,10 to use two similar lines rather than one for the information transfer. The first line carries (quasi)periodic clock SFQ pulses, and the second, the signal pulses. The binary unity/zero is represented by presence/absence of the signal pulse within a time interval between two neighbo-

ring clock pulses. This representation allows one to design  $^9,10$  a complete set of dc powered logic gates, including the NOR gate critical for virtually every Josephson junction logic family. Numerical simulation of these "Resistive Single Flux Quantum" (RSFQ) logic circuits has shown  $^9,10$  that they can operate at clock frequencies up to 30 GHz using externally shunted tunnel junctions with quite available  $I_cR$  products of order 300  $\mu$ V.

The purpose of this paper is to report the results of the experimental test of all basic components of the RSFQ logic circuits, including a universal gate which can perform the NOR function sufficient in principle for design of an arbitrary complex logic circuit.

### Test Circuit: General Structure

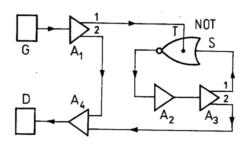

Figure 1 shows the general structure of our test circuit. Periodic SFQ pulses from the clock generator G are regenerated and split by the buffer/amplifier A1. Pulses from the port 1 of the amplifier serve to reset the NOT gate periodically. If no signal pulse arrives at the S input of the gate during a clock period, the gate produces an output pulse. Delayed by the stage A2 and split by the stage A3, this pulse arrives at the input S of the same gate. If the clock period T is not too short (is larger than the time delay T of this loop circuit) this pulse will block production of the output pulse during the next clock period. Thus the properly operating circuit produces the gate output pulses each second clock period. The buffer stage  ${\tt A}_4$  unites this pulse train with the original pulse train from the stage A1. Thus the average frequency of pulses arriving to the detector/load stage D equals  $(3/2)T^{-1}$ .

Fig. 1. Block structure of the experimental RSFQ test circuit: G, the SFQ pulse generator;  $A_1$  -  $A_4$ , the buffer/amplification stages; NOT, the RSFQ inverter; D, the SFQ pulse detector/load stage.

### Test Circuit: Design and Simulation

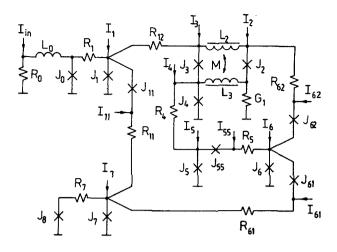

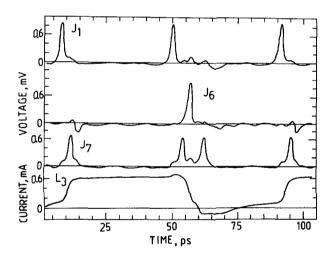

Figure 2 shows the equivalent circuit of our device, and Figure 3, results of its numerical simulations using the COMPASS program  $^{12}$  for experimental values of parameters and typical values of the dc bias currents  $\mathbf{I}_{in}$ ,  $\mathbf{I}_1$  +  $\mathbf{I}_7$ .

The clock generator G consists of the junction  $J_{\text{O}}$  biased by dc voltage  $V_{\text{O}}$  arriving from small resistor  $R_{\text{O}}$  through superconducting inductance  $L_{\text{O}}.$  The generated

Fig. 2. The equivalent circuit of the test structure. Crosses denote overdamped Josephson junctions; arrows, dc bias current leads.

Fig. 3. Results of numerical simulation of the circuit shown in Fig. 2 for the experimental values of its parameters: ( $I_{CO}=I_{C1}=I_{C6}=I_{C7}=1$  mA,  $I_{C4}=I_{C5}=0.75$  mA,  $I_{C11}=I_{C2}=I_{C3}=I_{C5}=I_{C61}=I_{C62}=0.5$  mA,  $I_{1}=I_{111}=I_{3}=I_{61}=I_{62}=I_{5}=0.4$  mA,  $I_{7}=0.93$  mA,  $I_{55}=I_{4}=I_{2}-I_{4}=0.2$  mA,  $I_{3}-I_{2}=0.28$  mA,  $I_{1}=I_{12}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13}=I_{13$

SFQ pulses following with the time period T =  $\Phi_0/V_0$  are passed to the buffer/amplifier  $A_1$  comprising two junctions  $J_1$  and  $J_{11}$ , dc biased below their critical currents. The arriving pulse induces  $2\pi$ -leap of the Josephson phase of the junction  $J_1$ , and is thus being reproduced with some gain. Junction  $J_{11}$  provides unilateral properties of the stage, i.e., prevents injection to  $J_1$  of pulses arriving from  $J_7$  (see below).

The NOT gate  $^{10}$  consists of a superconducting interferometer (including two Josephson junctions  $J_2,\,J_3$  and the mutually coupled inductances  $L_2,\,L_3)$  connected with junction  $J_4$  and resistor  $G_1.$  The interferometer has two alternative superconducting states differing by one flux quantum  $\varphi_0$  in its loop, i.e., by the direction of the persistent current circulating around the loop. Dependent on the initial state of the interferometer, the

arriving clock pulse induces the  $2\pi$ -leap of the phase of either junction  $J_3$  or  $J_4$ . In the latter case, an output pulse is developed across the junction  $J_4$ .

This pulse is delayed and regenerated by the buffer stage A2 comprising junctions J5 and J55, and is split by the stage A3 (J6, J61,J62); dynamics of these stages is similar to that of the stage A1. One copy of the pulse split by the stage A3 follows to the S input of the NOT gate through the resistor R62, while another copy arrives at the channeling amplifier A4 through the resistor R61. This amplifier A4 consists of the active junction J7 which regenerates the SFQ pulses arriving through both resistors R61 and R11, and of the circuit (R7, J8) which serves as a nonlinear passive load.

The SFQ pulses are very short and small (some 3 ps and 0.8 mV in our experiment), so that their direct observation presents a problem solvable only by rather complex techniques  $^{13}$ . Thus we have used a method traditional for this field  $^{6}$ ,7: to determine average frequencies  $f_{i}$  of the SFQ pulses in the given Josephson junction via measuring the dc voltage  $\overline{V}_{i} = \varphi_{0}f_{i}$  across it. According to the discussion of the previous section, in the properly operating test circuit the dc voltages across junctions should equal

$$V_0$$

, for  $J_1$ ,  $J_{61}$ ;

$(1/2)V_0$ , for  $J_2 - J_6$ ,  $J_{11}$ ; (2)

$(3/2)V_0$ , for  $J_7$ ;

within some range of the generator voltage  $V_{\rm O}$  starting from  $V_{\rm O}$  = 0. In practice, we measured dc voltages across  $J_1$ ,  $J_4$ ,  $J_5$ ,  $J_6$ ,  $J_{11}$ ,  $J_{61}$ , and  $J_7$  as functions of the bias current  $I_{\rm in}$  of the generator.

### Test Circuit: Layout and Technology

Figure 4 shows photographs of a central part of the test circuit before and after formation of the counter electrode. The layout was carried out using 10 µm design rules and in particular employs 10×10, 10×15 and 10x20 µm<sup>2</sup> active Josephson junctions. The original design based on the figure  $j_c = 0.1 \text{ kA/cm}^2$  for the critical current density of the Josephson junctions used only two superconducting layers, and a series of auxiliary large - area Josephson junctions providing superconducting pathes between the layers. Relatively large inductances (including those of the interferometer) were formed as strips of one electrode crossing gaps in the other electrode; distance between the strips forming L2 and L3 was calculated to provide their proper inductive coupling (M  $\simeq$  0.6L<sub>2</sub>). 200 µm

(a) (b) Fig. 4. Central section of the test circuit (a) before and (b) after deposition of the counter electrode.

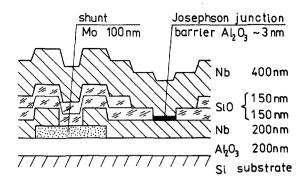

For fabrication of the circuit we used the Nb -  ${\rm Al}_2{\rm O}_3$  - Nb Josephson junction technology described in detail elsewhere <sup>14</sup>,15. Figure 5 shows (schematically) a cross section of a fragment of our thin - film structure. The structure was deposited onto silicon wafer

Fig. 5. Cross section of a representative part of the integrated circuit (schematically).

covered by a protective layer of  ${\rm Al}_2{\rm O}_3$ . The resistors were formed by chemical etching of Mo film with ( ${\rm R}_{\rm O}$ )4.2K  $\approx 1{\rm O}$ ; liftoff was used to pattern the upper layers. The Nb films were deposited using magnetron sputtering, and the SiO insulation, using thermal evaporation. After opening windows in the latter layer, the surface of the base electrode was RF cleaned and covered by thermally evaporated Al thin film. The film was then thermally oxidized 15 and the counter electrode was deposited. The Josephson junctions fabricated in this way exibited satisfactory small parameter scattering ( ${\rm Sj}_{\rm C}/{\rm j}_{\rm C} < 5{\rm N}$  throughout a chip), low leakage conductances ( ${\rm V}_{\rm m} > 10$  mV), and did not change their parameters after numerous thermal recyclings.

Unfortunatelly, the critical current density  $j_{\rm C}$  of the junctions at this first stage of experiments was close to 0.5 kA/cm², i.e., factor of five largerthan planned during the test circuit design. This is why it was found appropriate to deposit an additional insulating 0.5  $\mu m$  layer of the AZ 1350 photoresist and a Pb ground plane film over the whole structure. This measure reduced the inductances  $L_2$  and  $L_3$ , and thus the LI\_C product of the interferometer to the value 2.5  $\varphi_{\rm O}$  close to the planned one (~1.3 $\varphi_{\rm O}$ ). This is why the maximum clock frequency of the circuit, according to our numerical simulations (Fig. 3), should be close to 50 GHz, a factor of  $\sim$  1.7 less than could be achieved with same junctions for optimum values of the inductances.

## Experimental Results

The test circuit was activated at T = 4.2 K by consequent turning on of the dc bias of its stages, from the pulse generator to the detector. During this procedure the bias current of each stage was adjusted to provide its correct operation. In particular, turning out of the generator ( $I_{in} \rightarrow 0$ ) should stop propagation of the SFQ pulses along all the circuit, i.e., result in zero voltage across all its Josephson junctions.

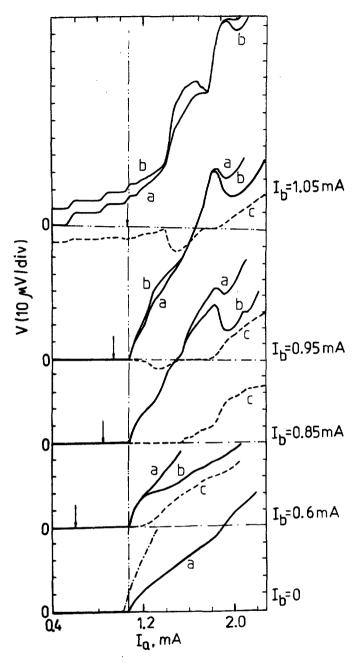

Figure 6 shows an example of such an adjustment for two neighboring stages a and b. If activated separately, the junctions of the stages exhibited I - V curves usual for overdamped junctions with close critical currents  $I_{\rm C}\simeq 1$  mA (the bottom plots). If the stage b was current biased somewhat below its  $I_{\rm C}$ , the dc voltage across it could be induced by the current  $I_{\rm A}>I_{\rm C}$ , partly because of the SFQ pulse generation, partly because of resistive coupling of the stages. When the former mechanism prevailed, the dc voltages across the Josephson junctions of the stages where exactly equal. Qualitatively, a close behavior can be observed at the usual mutual phase locking of the Josephson junctions  $^{16},^{17}$ , but one should remember that in our case the "locking" is strictly one-directional: the SFQ pulses (i.e., the highly nonsinusoidal Josephson oscillations) of the junction a with  $I_{\rm A}>I_{\rm C}$  induce the phase - locked pulses in the junction b with  $I_{\rm b}<I_{\rm C}$ , but not vice versa. When the both bias

Fig. 6. DC voltages across Josephson junctions of two neighboring stages (G and  $A_1$ ) of the circuit as function of one of the dc bias currents for several values of the second bias current. Dashed lines show the directly measured difference dc voltage  $V_c = V_a - V_b$ . Dash - dotted line shows  $V_b$  as the function of  $I_b$  for  $I_a = 0$ .

currents exceeded their critical values (see the top plots in Fig. 6), the phase locking could be observed as well, presumably of the mutual character here.

One can see that the SFQ reproduction in the stage b was especially stable at  $\rm I_b\simeq 0.85~mA$ , so that this value was fixed. True, the activation of the following stages required some readjustment of the previously established values of  $\rm I_i$ , but after some practice all dc currents could be properly fixed in few minutes.

In order to set up the bias currents  $I_2$  and  $I_3$ , the critical value of  $I_2$  was measured at first as a function of the difference current  $I_3$ - $I_2$  changing the flux bias of the interferometer. The operation point was fixed just below a minimum of this (periodic) dependence, thus

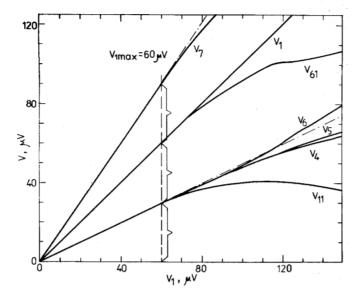

Fig. 7. Experimental plots of dc voltages  $V_i$  across various junctions of the test circuit versus  $V_i$  (see Fig. 2) obtained by slow sweeping of the generator current  $I_{in}$ . In the region 0 <  $V_1 \le 60$   $\mu V$  (0 < f  $\le$  30 GHz) where the relations (Eq 2) are fulfilled the test circuit is operating properly.

providing equal conditions for two stable states of the interferometer.

Figure 7 shows experimental plots of  $V_i$  vs  $V_l$  obtained by slow increase of the generator current  $I_{\rm in}$ . One can see that the proper relations (Eq 2) between the dc voltages are fulfilled exactly (at least within the experimental accuracy better than 0.5%) until  $V_l\simeq 60~\mu V$ , i.e., until the frequency of the generated SFQ pulses f  $\approx 30~{\rm GHz}$ . According to the both experimental and simulation results, at this frequency the channeling stage  $A_4$  becomes too refractorary due to somewhat improper choice of its parameters.

# Conclusion

We have successfully demonstrated operation of a test circuit including all basic components of the RSFQ logic family at signal frequencies up to  $\sim 30$  GHz. This encouraging result was obtained despite very simple layout of the circuit (two superconducting layers), large minimum feature size (10  $\mu$ m), and a value of the critical current density far from the planned one.

Moreover, the further analysis have shown <sup>11</sup> that a considerable improvement of the RSFQ logic performance is possible owing to replacement of the coupling resistors by the Josephson junctions, and some modification of the logic gates. Accompanied by use of the modern junctions <sup>17-19</sup>, these improvements can presumably allow one to create dc - powered high - density (~10<sup>-6</sup> cm<sup>2</sup>/gate) digital integrated circuits with extremely high clock frequencies (up to 400 GHz), and moderate power consumption (of order 10<sup>-6</sup> W/gate). We believe that these factors make the RSFQ logic family the most promising one in the whole Josephson junction digital technology.

## Acknowledgements

Useful discussions with Zh. I. Alferov, K. A. Valiev and E. P. Velikhov are gratefully acknowledged.

#### References

- K. Nakajima, Y. Onodera, and Y. Ogawa, J. Appl. Phys., 47, 1620-1627, 1976.

- T.A. Fulton, R.S. Dynes, and P.W. Anderson, Proc. IEEE, 61, 28-35, 1973.

- 3. K.K. Likharev, IEEE Trans. Magn., 13, 245-247, 1977.

- K.K. Likharev, S.V. Rylov, and V.K. Semenov, IEEE Trans. Magn., 21,947-950, 1985.

- J.P. Hurrell, D.C. Pridmore-Brown, and A.H. Silver, IEEE Trans. El. Dev., 27,1887-1896, 1980.

- C.A. Hamilton and F.L. Lloyd, IEEE E1. Dev. Lett., 3, 335-338, 1982.

- A.H. Silver, R.R. Phillips, and R.D. Sandell, IEEE Trans. Magn., 21, 204-207, 1985.

- K. Nakajima, G. Oya, and Y. Sawada, IEEE Trans. Magn., 19, 1201-1204, 1983.

- O.A. Mukhanov and V.K. Semenov, Preprint, Phys., Moscow State Univ., No. 9, 1985.

- 10. K.K. Likharev, O.A. Mukhanov, and V.K. Semenov, pp. 1103-1108, in SQUID'85, H.D. Hahlbohm, H. Lübbig, Eds., Walter de Gruyter, Berlin, 1985.

- 11. O.A. Mukhanov, V.K. Semenov, and K.K. Likharev, "U1timate Performance of the RSFQ Logic Circuits", Rept. No. EC-28, this conference.

- 12. V.K. Semenov and V.P. Zavaleev, "Automation of Numerical Analysis of Superconducting Networks", Rept. No. LE-28, submitted to ASC-84, unpublished.

- P. Wolf, B.J. Van Zeghbroeck, and U. Deutsch, IEEE Trans. Magn., 21, 226-229, 1985.

- 14. M. Guzwitch, M.A. Washington, H.A. Huggins, and J.M. Rowell, IEEE Trans. Magn., 19, 791-794, 1983.

- 15. V.P. Koshelets, G.A. Ovsyannikov, I.L. Serpuchenko, S.V. Shitov, and A.N. Vystavkin, Pisma Zh. Tekh. Fiz., 11, 290-295, 1985 [Sov. Phys.- JTP Lett.].

- A.K. Jain, K.K. Likharev, J.E. Lukens, and J.E. Sauvageau, Phys. Repts., 109, 309-426, 1984.

- 17. L.E. Amatuni, V.N. Gubankov, S.A. Kovtonyuk, V.P. Koshelets, G.A. Ovsyannikov, I.L. Serpuchenko, and A.N. Vystavkin, "Josephson Junctions with Silicon Interlayer and Arrays", Rept. No. EC-5, this conf.

- E.G. Hu, R.E. Howard, L.D. Jackel, L.A. Fetter, and R.H. Bosworth, Appl. Phys. Lett., 35, 879-881, 1979.

- 19. A.L. Gudkov, K.K. Likharev, and V.I. Makhov, Pisma Zh. Tekh. Fiz., 11, 1423-1427, 1985 [Sov. Phys. -JTP Lett.].